# **Electrical Plus Functional Testing Approach in Designing Electronics That Survive Harsh Conditions**

Mike Bixenman, DBA, Bobby Glidwell Magnalytix, LLC TN, USA mbixenman@magnalytix.com

Terry Munson, Paco Solis, Jim Gryga, & Steve Middleton Foresite, Inc. IN, USA

#### ABSTRACT

Electronic device reliability is more challenging due to various factors related to increased functionality, component miniaturization and design, materials, assembly process, and the demands of the user environment. Factors such as ambient humidity and temperature conditions, day/night temperature variations, cleanliness of the electronic circuitry, PCBA design, and surface characteristics all influence device reliability.

Advanced technologies across many fields rely on electronic and software functions that perform on demand. Most reported failures arise from process-related contamination reacting with the operational environment, creating latent failures from the remaining trapped residues on the PCBA surface after the soldering operations.

This paper proposes a new test method and test vehicle to characterize soldering materials, assembly process steps, and conformal coating to determine the reliability of a device.

Key words: Process Residues, Climatic Reliability, SIR Testing, Functional Testing

# INTRODUCTION

The present SIR and Electrochemical Migration (ECM) electrical test methods for soldering materials do not address the electrochemical failure mechanism concerns of flux residues trapped under component terminations, modern materials, and the ever-shrinking spacing between solder joints.<sup>[1]</sup> The combined variables of multiple attach technology processes can directly contaminate the assembly. New test vehicles are needed to test soldering, process, and cleaning materials to determine the electrochemical reliability of the remaining flux residue and tighter board spacing.<sup>[1]</sup>

As component pitch reduces in size, leadless packages increase, and high-density / high-impedance designs become more commonplace.<sup>[2]</sup> Failure mechanisms are based on mechanical, electrical, thermal, and chemical processes. The degree of risk requires understanding the drivers and physical mechanisms that cause electrochemical migration to occur.

Accelerated corrosion is driven by contamination through the assembly and soldering steps. The amount, distribution, and morphology of flux residue vary considerably with specific soldering processes and parameters.<sup>[3]</sup> The active ingredients within the flux residue may exhibit a high deliquescence for climatic moisture, thereby increasing leakage currents resulting in intermittent or permanent failures.

#### **PROBLEM STATEMENT**

Electronic hardware failure occurs for various reasons, and a common one is electrochemical migration (ECM).<sup>[4]</sup> The problem is that process contamination, most notably flux residue causes leakage currents and shorts between leads, pads, and vias.

A variety of factors and residue sources contribute to the underlying cause, including bare board and component cleanliness, incomplete heat-activation of no-clean fluxes, poor cleaning system performance, flux and/or cleaning agent entrapment under low standoff component packages, wave and selective flux migration, manual and rework soldering, and topical cleaning.<sup>[4]</sup>

Current SIR methodologies look for changes in a set of welldefined architectural patterns. While these test architectures are very useful for judging the material behavior in a set of finite variables, they do not inherently account for the multiple formations that parasitics and dendrites form across adjacent assembly technologies (i.e., Pad-to-Pad, Pad-to-Hole, and Hole-to-hole-architectures).

There is a need for additional and advanced tools to help bridge the data gap between SIR test methodologies and the way electronic failures are generated in actual hardware. To bridge this gap can help to associate the relationship of SIR and issues encountered in Field Service hardware.

# PURPOSE OF THE RESEARCH

Designing test vehicles and test instrumentation that detect changes in electrical characteristics due to contamination on the circuit assembly that may lead to failure is needed. The IPC B-24 and B-25A have not kept up with the challenges of modern electronics assembly.<sup>[1]</sup>

As circuitry miniaturizes, component pitch narrows. Bottom Terminated Packages with signal and power connections close to large ground connections trap large deposits of flux residue. These large ground connections are needed to remove heat produced by the component. These components have very small clearances between the bottom of the component and the circuit board. This creates a good environment for electrochemical migration and dendrite growth, particularly in harsh service environments.

In addition to the surface mount components, test board designs need test sites to monitor secondary process steps to build the final assembly.<sup>[4]</sup> Wave and selective soldering fluxes can wet neighboring components. Improper flux heat activation leaves behind ionic flux residues. Wave and selective pallets can inhibit proper heat activation, allowing the flux to flow into thermally protected isolation areas, leaving an active flux. Manual and rework soldering can transfer residues via localized brushing, solvent cleaning, and poor rinsing. Manual application of tacky paste flux is subject to excess material deposition or placement in areas where proper thermal activation is difficult. Partial cleaning, bath life, and rinsing can leave problematic ionic residues. A test vehicle and test instrument designed to evaluate real process conditions gives the process engineer a meaningful assessment of their assembly process.

Having additional tools which can bridge the gap between SIR and functional hardware would help to drive effective design, material, and process changes for the electronics industry.

#### SURFACE INSULATION RESISTANCE (SIR)

SIR detects the effects of ionic residues that can cause intermittent and total failure. SIR testing uses an industrystandard pattern of traces (called a comb) to test the conductivity of process residues by combining environmental moisture, temperature, and bias voltage in a test chamber and monitoring electrical resistance over 7-days.

Figure 1: SIR Comb Structure between the Positive and Negative Inner connections

SIR measures insulation resistance in the form of current. Resistance is the opposition of current flow in an electrical current.<sup>[6]</sup> Conductors such as lead, tin, copper, silver, and gold offer very little resistance, thus allowing current to move easily in and out of the conductive pathways. SIR is an electrical property that measures leakage currents due to ionic contamination, reducing electric current flow. The higher the surface insulation resistance value, the lower the risk of field failures.

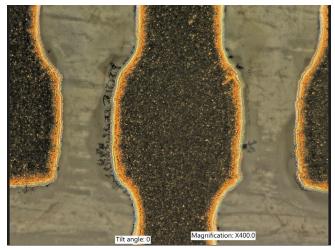

Climatic conditions (temperature and humidity) directly impact an electronic device's functioning, lifetime, and overall reliability.<sup>[5]</sup> An increase in relative humidity (RH) is known to increase the corrosion rates of metals.<sup>[6]</sup> Active and ionic residues on the PCB surface and under component terminations hydrogen bond with water to form leakage currents when the circuit assembly is exposed to high humidity. Figure 2 shows small dendrites growing from the cathode toward the anode. These leakage currents cause a sudden or gradual drop in surface insulation resistance.

Figure 2: Leakage Currents

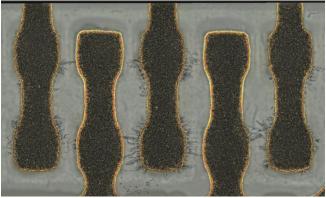

Leakage currents are involuntary currents that flow across conductors of opposite polarity. As resistance drops to the ground, metal oxides are aligned. Metal oxides form dendritic growth patterns that can lead to no found faults. When these metal dendrites grow from the cathode to the anode, resistance flat lines to the low-level resistor value  $6 \text{ Log}10\Omega s$ , which results in a dead short (device failure).

Figure 3: Dead Short

The threshold RH for the SIR failures in circuitry is greatly affected by the type and amount of ionic contamination present on the printed circuit board assembly. Solder flux residues are the major source of ionic contamination on the manufactured PCBA, with the corrosiveness being a function of the activator type used in the flux composition.<sup>[5]</sup> The actual safe level of contamination for a specific PCBA will depend on the sensitivity of electronic circuits to the reduction of SIR, which is a function of RH (device exposure conditions), and the physical properties of the contaminants, i.e., adsorption, absorption, and solubility in water; ionic conductivity; and temperature dependence.<sup>[5]</sup>

SIR is the "gold standard" for determining the effects of process contamination. Newer test board designs with sensitive components allow OEMs, designers, and assemblers to select safe materials and optimize their assembly process. These steps ensure a quality product that will perform on demand within harsh climatic environments.

# **RESEARCH QUESTION**

SIR testing has a limitation in that it does not test the effects on live hardware. When leakage currents are present, how does this corrosion impact the functional circuits? How would one design a test board that allows the design authority to understand the functional side when insulation resistance drops due to process contamination?

# **RESEARCH HYPOTHESIS**

The research hypothesis in this study expects a functional component performance change (lag - over biasing - under biasing) when surface insulation resistance drops due to the formation of leakage currents.

# FUNCTIONAL TESTING

Functional tests examine the entire assembly rather than individual components. The tests simulate the final electrical environment where the PCB will reside. During SIR testing, functional components are tested independently against a program model containing parameters specific to the component and its functionality. Each function is compared to the corresponding requirement to ascertain whether its output meets the end user's expectations.

Power electronics include power train control, sensors, and information modules that require time-consuming transfers of large data files.<sup>[7]</sup> The strength of SIR testing is the ability to characterize materials and processes to determine acceptable levels of process contamination. The research hypothesis infers that functional testing with SIR testing on the same test vehicle enables reliable testing at the lowest price possible.

The researchers are trying to prove that functional plus SIR combination testing is a dynamic rather than static test platform. Does functional testing in combination with SIR testing in a known environment enable a circuit designer to test surface mount, selective, and manual soldering to obtain results that correlate with performance expectations? It is well known that miniaturized components combined with high-density circuitry increase field failures when active flux residues are on the circuit card. Will this test approach provide a cost-effective way to catch defects related to problematic contamination?

# FUNCTIONAL / SIR TEST VEHICLE

The test board is designed with functional, CAF and SIR test circuits monitored under power. The test assembly is a tool to understand the material effects under SIR conditions using different component structures. The test board is designed to test for the interactive effects of the collective residues from multiple soldering steps, whether No-Clean or Cleaning, on functional circuits and their interactivity in typical operation conditions. This shows why a short in one area will crash a separate part of the circuit with just a few ohms of leakage on sensitive circuits that may or may not recover. SIR misses the effect of circuit sensitivity on functional performance, and this test vehicle is the first step to creating this understanding.

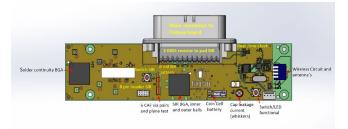

The front side of the test board design in Figure 4 contains the following components.

- SIR components

- 8-pin SIR header

- BGA, inner and out balls

- $\circ$  2 (0805) resistors to SIR pad

- 6 CAF via pairs and plane test

- Functional components

- Solder continuity BGA

- Coin cell battery

- o RF Wireless circuit and antenna

- Real-time clock

- Temperature Monitor

- o Humidity Monitor

- o Switch/LED

- Cap leakage current (whiskers)

Figure 4: Front side of the Functional / SIR Test Board

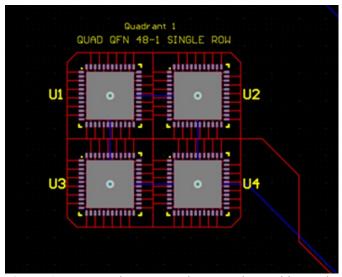

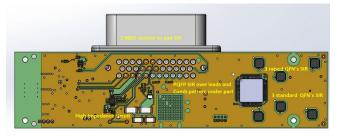

The back side of the board design in Figure 5 contains the following components.

- SIR Components

- o 2 (0805) resistors to SIR pad

- PQFP SIR over leads and Comb pattern under part

- 3 raised QFNs

- 3 standard QFNs

- Functional Component

- High Impedance Circuit

- o Core Voltage Circuit Monitoring

Figure 5: Back side of the Functional / SIR Test Board

# DATA COLLECTION

The identifier/location assigned to each component during testing is a crucial reference point for determining the circuit board's X, Y, and Z (Front/Back) coordinates. These coordinates are used to precisely locate and display an image of the circuit board, facilitating visual inspection and analysis of individual components within the context of the entire board.

# Criteria

- 1. Binary: This criterion involves a simple pass/fail outcome. It's typically used when there is a clear yes/no, on/off, or true/false condition to evaluate.

- 2. Range: This criterion involves checking whether a numerical value falls within a specified range or interval. Once the minimum and maximum value is established, the status is determined based on whether the actual value falls within the range.

- 3. Maximum: This criterion sets a maximum allowable value for a numerical parameter. If the actual value exceeds this maximum, it triggers a specific status.

4. Minimum: This criterion establishes a minimum required value for a numerical parameter. If the actual value is below this minimum, it results in a particular status.

|--|

| Component   | Min.        | Max.  | Unit | Criteria | Warning |

|-------------|-------------|-------|------|----------|---------|

| Battery     | 1.3         | 3.6   | V    | Standard | 5%      |

| Voltage     |             |       |      |          |         |

| 250µF       | 0           | 35    | mA   | Standard | 5%      |

| Capacitor   |             |       |      |          |         |

| Leakage     |             |       |      |          |         |

| Current     |             |       |      |          |         |

| High        | 200         | 230   | mA   | Standard | 5%      |

| Current     |             |       |      |          |         |

| 3.3 V Rail  | 3.135       | 3.465 | V    | Standard | 5%      |

| Temperature |             |       | °C   | Custom   | 5%      |

| Humidity    |             |       | %    | Custom   | 5%      |

| Main        | 100         |       | Ω    | Standard | 5%      |

| Connector   | $meg\Omega$ |       |      |          |         |

| SIR         |             |       |      |          |         |

| BGA Outer   | 100         |       | Ω    | Standard | 5%      |

| SIR         | megΩ        |       |      |          |         |

| BGA Inner   | 100         |       | Ω    | Standard | 5%      |

| SIR         | megΩ        |       |      |          |         |

| Switch SIR  | 100         |       | Ω    | Standard | 5%      |

|             | megΩ        |       |      |          |         |

| Comb SIR    | 100         |       | Ω    | Standard | 5%      |

|             | megΩ        |       |      |          |         |

| 8-pin       | 100         |       | Ω    | Standard | 5%      |

| connector   | $meg\Omega$ |       |      |          |         |

| SIR         |             |       |      |          |         |

| Probe SIR   | 100         |       | Ω    | Standard | 5%      |

|             | megΩ        |       |      |          |         |

| QFN1 SIR    | 100         |       | Ω    | Standard | 5%      |

|             | megΩ        |       |      |          |         |

| QFN2 SIR    | 100         |       | Ω    | Standard | 5%      |

|             | megΩ        |       |      |          |         |

| PQFP SIR    | 100         |       | Ω    | Standard | 5%      |

|             | megΩ        |       |      |          |         |

| CAF Via     | 100         |       | Ω    | Standard | 5%      |

| Resistance  | megΩ        |       |      |          |         |

| BGA Solder  |             | 500   | Ω    | Standard | 5%      |

| Joint       |             |       |      |          |         |

Clarifications:

- Standard is a criterion that is defined.

- Custom is criteria set per test or defined by the user.

- The user defines a warning trigger.

- Binary criteria are non-customizable and rely on the straightforward assessment of whether a signal is received.

# TESTING

Parameters are set on a per-test basis. These parameters are tailored to the test's particular requirements and characteristics.

Table 2: Metrics

| Name          | Туре    | Unit       | Notes |

|---------------|---------|------------|-------|

| Name          | String  | Short      |       |

| Description   | String  | Long       |       |

| Test Duration | Number  | Hour       |       |

| Test Voltage  | Number  | Volts      |       |

| Sampling Rate | Number  | S          |       |

| Temperature   | Number  | °C         |       |

| Humidity      | Number  | %          |       |

| Cycling       | Boolean | True/False |       |

### **Test Startup**

- 1. **Parameter Review:** A comprehensive review of the test parameters is performed. This entails verifying that the selected parameters align with the specific requirements of the test, including any variations required for individual test cases.

- 2. Board Configuration Check: Confirmation of the test board or equipment configuration is undertaken. This step ensures that the board setup matches the intended configuration for the test, including the placement and connections of components.

- **3. Equipment Setup Verification:** Detailed instructions for verifying all testing equipment's setup and functionality are reviewed. This process ensures that all equipment is correctly configured and calibrated for accurate testing.

- 4. Start Test: The test is initiated once the above steps are satisfactorily completed. This involves the actual execution of the testing process, following the predefined parameters, board configuration, equipment setup, and any specified testing instructions.

# **Test Assumptions**

- 1. Components in a Group: It is assumed that components within the same group are intended to be viewed together for statistical analysis, charting, and other purposes.

- 2. Error State Priority: When determining the overall group status, it is assumed that any component in an error state takes priority, and the group's status reflects this error state. In other words, an error in one component affects the entire group's status.

- **3. Isolation of Component Groups:** Components from different groups do not need to be viewed together by default. This suggests that the UR design separates component groups, making it easy for users to focus on one group at a time.

- 4. Custom Chart Builder Exception (Numeric/Binary Separated): While components from different groups do not need to be viewed together by default, there is an exception for a custom chart builder. It is assumed that the custom chart builder allows users to select components from different groups and create custom charts or visualizations if needed.

- 5. Real-Time Data: This UI assumes that real-time data updates are essential for monitoring and analyzing the components' performance during the test.

- 6. User-Friendly Navigation: The UI has userfriendly navigation options that allow users to seamlessly switch between different component groups by functional test block or return to the main dashboard.

- 7. Criteria Customization: While not explicitly mentioned, it can be inferred that the UI allows users or administrators to customize the criteria used for evaluating component performance.

- 8. Historical Data Availability: The UI assumes that historical data is available and can be visualized in chart form for each component's test.

#### Dashboard

| Item                  | Description                                | Y/          |

|-----------------------|--------------------------------------------|-------------|

| 1.011                 | Description                                | N           |

| Overall Test          | The overarching status of the entire       | Y           |

| Status                | test indicates its progress issues.        |             |

| General Test          | Key details about the test include         | Ν           |

| Information           | name, ID, duration, and environment.       |             |

| Time to Next          | Countdown timer indicating the             | Y           |

| Measurement           | time remaining until the next measurement. |             |

| Current               | Indicates whether the test is actively     | Y           |

| Measurement<br>Status | measuring or temporarily paused.           |             |

| Component             | The status of component groups is          | Y           |

| Groups                | visualized with traffic light colors       |             |

|                       | (e.g., green for passing).                 |             |

| Number of             | Count of components failing the test       | Y           |

| Failures              | within each group for issue                |             |

|                       | identification.                            |             |

| Individual            | Status of each component, including        | Ν           |

| Component             | name, test result, and visual              |             |

| Status                | indicator.                                 |             |

| Progress Bar          | Visual representation of overall test      | Y           |

|                       | progress, displaying completion            |             |

|                       | percentage.                                |             |

| Log and               | Display of error messages,                 | Y           |

| Alerts                | warnings, or alerts generated during       |             |

| D.                    | the test.                                  | <b>N</b> .T |

| Data                  | Graphical presentation of historical       | Ν           |

| visualization         | test data via charts or graphs             |             |

| Real-time             | Real-time updating of all                  |             |

| updates               | monitoring factors for instant feedback.   |             |

| Test Controls         | Controls for starting, stopping,           |             |

|                       | pausing, or resuming the test as           |             |

|                       | needed.                                    |             |

#### **Individual Component Groups**

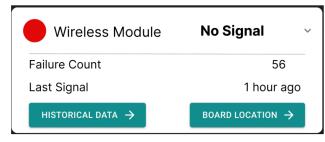

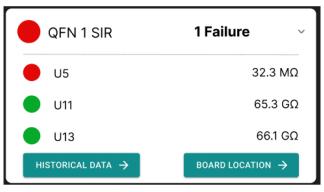

1. Traffic Light Indicator: The visual indicator displays the overall status of the component group,

using colors such as green (all components passing), yellow (some components failing), or red (all components failing).

- 2. Component Group Name: Indicates the name or identifier of the component group for quick identification.

- **3. Group Quick Detail:** A count shows how many components are in the group and how many are currently failing (Only applies to groups with more than one component).

- 4. Expandable Component List: If the group contains more than one component, an icon button with a dropdown is provided. Clicking on this button reveals a list of each component within the group. Each component entry displays its name and a visual indicator (e.g., traffic light color) to show its status.

- 5. Detailed View: A clickable option is available to access more detailed information for component groups with only one component or when viewing an individual component. Clicking this option opens a detailed view that provides access to:

- **a. Historical Data:** A chart or graph representing historical data related to the component's performance. This chart may include trends, statistics, and historical results.

- **b. Detailed Statistics:** Specific statistics and metrics related to the component's performance during the test.

- c. Interactive Controls: Controls for interacting with the component, such as starting or stopping individual component tests or making configuration adjustments.

- **d.** Logs and Alerts: Access to error messages, warnings, or alerts generated by the individual component.

Figure 6: Failure Warning Indicator

Figure 7: QFN SIR Status

# **Component Group View**

- 1. Component Group Name: Displays the name or identifier of the component group to which the component belongs, providing context.

- 2. Component Name: Indicates the name or identifier of the individual component under test within the group, allowing for specific identification.

- **3.** Component Location: Lists the location or position of each component within the test setup, helping users locate it physically.

- 4. Component Location Image: Provides a visual representation or image of the test setup with markers or labels indicating the physical location of each component.

- 5. General Statistics

- **a.** Number of Readings: Displays the total number of readings or measurements taken for the component since the test began.

- **b.** Errors: Indicates the number of errors or issues encountered during testing.

- **c.** Time Under Test: Shows how long the component has been undergoing testing since the start.

- 6. Overall Status for Component Group: A visual indicator (e.g., traffic light color) that represents the overall status of the component group to which the individual component belongs. This indicator considers the status of all components within the group.

- 7. Individual Status for Each Component: Separate visual indicators (e.g., traffic light colors) for each component, such as pass/fail or specific conditions.

- 8. Measurement History Chart: A chart or graph displaying the full history of measurements for the component test. This chart visually represents how measurements have changed over time, allowing users to identify trends or anomalies.

- **9.** Criteria Definition: Clear and concise information about the criteria used to evaluate the component's performance and determine its pass/fail status. This may include threshold values, ranges, or other relevant criteria.

- 10. Navigation Options: Navigation buttons or links allow users to easily switch between different

components within the same group or return to the main dashboard.

# **General Stats**

- 1. Criteria Type (Max/Min/Range): Indicates the criteria used for evaluation.

- Example: Range

- 2. Criteria Values: Specifies the specific values or thresholds for the criteria.

- Example: Minimum Value: 20, Maximum Value: 80

- **3.** Number of Readings: The total readings or measurements taken during the test.

- Example: 500 readings

- 4. **Percent/Count Pass**: The percentage or count of readings that meet the pass criteria.

- Example: 95% pass rate, 15 readings failed

- 5. Percent/Count Fail: The percentage or count of readings not meeting the pass criteria.

- Example: 3% fail rate, 15 readings failed

- 6. Percent/Count Warning (optional): The percentage or count of readings within a warning range.

- Example: 2% warning rate, 10 readings within the warning range.

- 7. Time for First Error: The timestamp or duration from the test start when the first error occurred.

- Example: The first error occurred 15 minutes into the test.

- 8. Total Time Under Test: The component or system's cumulative duration under test.

- Example: Total test duration was 4 hours and 30 minutes.

- **9. Standard Deviation:** A measure of the dispersion, variability, or readings.

- Example: Standard deviation of 5.3

#### Charting

1. **Binary Data:** A binary spectrum chart represents errors or anomalies occurring over a specific period. This chart presents binary data with two distinct states: error and numerical operation.

Figure 8: Example of Binary Chart

- 2. Numeric Data

- a. **Passing Range:** Data points within this range are acceptable.

- b. **Warning Range:** Data points within this range indicate a potential issue that may require attention.

- c. **Failing Range:** Data points within this range signify a critical deviation from the expected values and demand immediate attention.

# **PATH FORWARD:**

To properly assess the effects of process residues during manufacturing, the industry needs additional tools (beyond visible inspection and periodic ROSE testing) that measure active circuity change when exposed to environmental conditions. Assessing residues during the manufacturing with SIR (surface insulation resistance) compared to functional circuitry on the same assembly determines the interactive effects of the process. This allows understanding of IPC SIR limits to critical sensitive circuits, LED, battery, clock, high impedance, microprocessor high speed, and RF circuits.

# CONCLUSION

The test assembly and instrumentation are tools designed to understand the material effects under SIR conditions of different component structures, along with the interactive effects of the collective of residues from the multiple soldering/cleaning or soldering and No-Clean operation on the functional circuits and their interactivity in typical operation conditions. The goal is to show the effect of why a short in one area will crash a separate part of the circuit with just a few ohms of leakage or sensitive circuits that may or may not recover. SIR misses the effect of circuit sensitivity on functional performance. The test vehicle design is the first step to creating this understanding.

# FOLLOW ON RESEARCH

The next step is to validate or reject the research hypothesis. The researchers plan to build the Functional/SIR test vehicle with soldering materials across IPC classifications. The plan is to present these findings at industry conferences in the coming months.

#### REFERENCES

- Tellefsen, K. (2015), SIR and ECM Testing of Soldering Materials vs. Soldering Processes. SMTAI, Rosemont, IL.

- 2. Bumiller, E. & Hillman C. (n.d.) A Review of Models for Time-to-Failure due to Metallic Migration Mechanisms. DfR Solutions, College Park, MD

- Helene, C., Jellesen, M.S., Verdingovas, V. & Ambat, R. (2013). Decomposition studies of no-clean solder flux systems in connection with corrosion reliability of electronics. EUROCORR (2013). European Corrosion Congress.

- 4. Munson, T. (2021). The Forensics of Dendrite Shorting. Foresite, Inc. Kokomo, IN.

- Verdingovas, V., Joshy, S., Jellesen, M., & Ambat, R. (2016). Analysis of surface insulation resistance related failures in electronics by circuit simulation. Circuit World, Number 2, 2017, 45-55.

- 6. Wikipedia (2023). Electrical Resistance and Conductance. Retrieved from Electrical resistance and conductance Wikipedia

- 7. Keysight Technologies. (n.d.). The benefits of using LAN extensions for instrumentation in Automotive Functional Test.